随着半导体技术的不断进步,门阵列(Gate Array)作为一种应用专用集成电路(ASIC)设计制造的创新方式,曾经在电子产业尤其是上世纪八十年代风靡一时。门阵列技术基于预先制造好的芯片,将绝大多数晶体管空白预留,通过后期金属互连层定制连接,构筑成特定的逻辑功能。这样既降低了非重复性工程成本,也提高了设计与制造的效率,成为半定制芯片中的代表。回顾门阵列的发展历程,可以看到它在技术创新、产业演变和市场竞争上的重要地位,并且其设计理念对于现代芯片制造依然具有启示意义。 门阵列技术的起源可以追溯到上世纪七十年代,当时,随着电子设备对集成电路性能和功耗的需求不断增长,传统的全定制芯片设计方法日益暴露出周期长、成本高的劣势。由此,预制芯片上通用晶体管阵列的思路被提出,即先完成晶体管层的制造,后续根据客户需求在金属连接层实现逻辑功能的定制。

英国的Ferranti公司在这一领域领先,推出了以双极型晶体管(bipolar transistor)为基础的未指定逻辑阵列(Uncommitted Logic Arrays,简称ULA),实现了千级至万级门电路的设计应用,尤其广泛应用于相机和通信设备领域。 然而,早期的门阵列技术由于使用双极工艺和光刻层数限制,导致性能较低、成本较高。直到CMOS技术的引入,门阵列才迎来爆发式发展。CMOS技术不仅带来了更低的功耗和更小的芯片面积,也使得门阵列设计趋向自动化。1974年,Robert Lipp等人率先采用7.5微米工艺制造出了第一批CMOS门阵列芯片,该设计融合了n型和p型晶体管的严格排列和金属层基于网格的互连结构,这些创新为未来全自动化设计铺平了道路。 门阵列的设计理念自然映射到电路自动化软件的发展上。

早期的设计依靠手工绘制和覆盖技术实现,随着计算机辅助设计(CAD)技术的兴起,门阵列的设计效率显著提升。特别是LSI Logic公司成立后,推出了基于5微米双层金属工艺的全自动门阵列设计流程,为用户提供远程登录设计系统,实现客户自主芯片设计,从而降低了准入门槛和设计周期,极大促进了门阵列市场的繁荣。 门阵列的创新优势主要体现在成本控制和快速交付上。预制晶圆库存的策略使得掩模制作和测试夹具的非重复费用大大降低,产品周期相比全定制芯片缩短至数周。其适中性能和足够的逻辑密度满足了许多低功耗、便携式和航天领域的应用需求。典型案例如英国的Sinclair ZX81家用计算机,使用ULA芯片极大简化了原有复杂的电路设计。

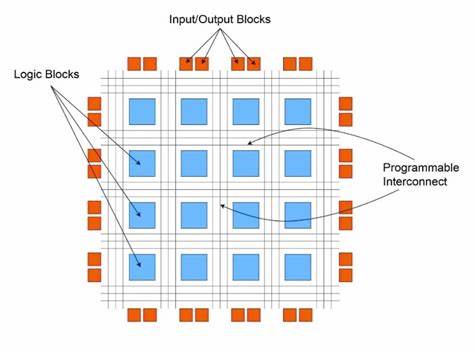

此外,如BBC Micro、Acorn Electron和Commodore Amiga等知名计算机产品也大量采用门阵列,提升设备集成度和成本效益。 门阵列面临的挑战源于集成度和性能限制。由于绝大多数晶体管结构已被固定,设计者难以对晶体管本身进行优化,只能凭借金属层互连完成逻辑实现,导致芯片密度与速度在高要求场景下有所欠缺。相比标准单元设计与全定制芯片,门阵列的灵活性和性能表现具有明显劣势。随着摩尔定律推进和工艺升级,功能更强大的标准单元ASIC以及可编程逻辑器件相继出现,对门阵列市场形成巨大冲击。 另一个改变市场格局的技术是场可编程门阵列(FPGA)。

作为一种用户可反复编程的逻辑器件,FPGA免去了掩模定制的高昂费用,且设计验证周期极短,逐渐取代小批量门阵列设计应用。尽管高端FPGA依然面临功耗大、速度慢以及成本高的限制,FPGA到ASIC的转换服务的发展也缓解了这一矛盾,使得门阵列技术获得了一定的新生机会。 在全球市场竞争背景下,门阵列产业经历了兴衰起伏。英国、美国和日本等国家都曾涌现出多个重要厂商,其中如Ferranti、LSI Logic和International Microcircuits等公司推动了技术与市场的发展。许多厂商通过引入复杂设计自动化工具,例如Ferranti的ULA Designer和Silicon Design System,缩短设计周期,提升设计质量。然而,产业的周期性波动和利润压缩使部分企业被迫退出,技术交由大型半导体公司整合或被FPGA和标准单元ASIC分食。

门阵列在设计实施过程中具备高度的可控性。芯片厂商通常提供不同规格的标准门阵列芯片波段,设计者需根据逻辑门数、输入输出引脚数量以及布线需求选择最适合的型号。由于布线复杂度对成本和性能影响显著,厂商会通过租特法则(Rent’s Rule)等经验模型预测布线密度。设计时需权衡逻辑资源利用率及路由余量,以保持合理的成本与性能平衡。 展望未来,尽管门阵列已不再是ASIC设计的主流,但其理念仍影响着现代半导体设计流程。结构化ASIC的兴起借鉴了门阵列的预制逻辑模块配合后期定制连接的思路,实现功能更丰富且设计自动化程度更高的芯片。

同时,在新兴应用如低功耗物联网设备和特定工业控制领域,定制门阵列结合先进工艺依旧具有一定竞争优势。结合先进设计软件和生产自动化技术,门阵列仍有望在特定市场细分中焕发活力。 综上,门阵列作为半定制ASIC设计的重要方法,通过预制晶体管阵列加后期金属层互连实现灵活设计,曾经推动了电子产业特别是家用计算机和通信设备的快速发展。虽然其市场份额逐渐被FPGA和全定制ASIC侵蚀,但门阵列西恩的技术创新和设计方法对现代集成电路设计产生了深远影响。未来结合新工艺和自动化工具,门阵列将在低功耗、高集成度和快速交付应用中继续发挥价值,成为半导体技术历史中不可或缺的重要篇章。