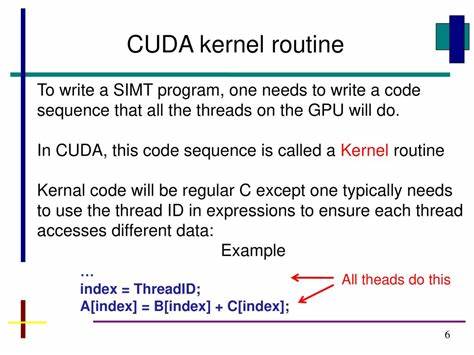

随着人工智能、大数据和高性能计算的快速发展,GPU并行计算技术正逐渐成为计算领域的主流解决方案。而在众多并行计算平台中,英伟达推出的CUDA(Compute Unified Device Architecture)以其强大的性能和灵活的编程模型,吸引了大量开发者投身其中。特别是CUDA内核编写(Kernel Writing),作为CUDA编程的关键环节,决定了程序的性能瓶颈和优化空间。深入理解CUDA内核编写的技术要点,对于开发高效的GPU计算应用至关重要。 CUDA内核是指在GPU上执行的函数,它们通过并行方式运行在成千上万个线程中,实现数据并行处理的目标。编写CUDA内核的第一步是明确并行计算的任务划分,将应用中的计算任务分解成适合并行执行的线程。

每个线程处理不同的数据片段,从而实现大规模数据的高速处理。线程的数量和组织形式通常由线程块(block)和线程网格(grid)结构定义,这种层级结构不仅支持海量线程的管理,也方便开发者进行性能调优。 内核函数的设计原则之一是最大限度地利用GPU的计算单元和内存带宽,减少线程之间的依赖和同步。内核中每个线程执行相同的指令,但计算的数据不同,这种单指令多数据(SIMD)架构保证了GPU在执行大规模数据并行任务时的高效率。然而,线程之间的通信和同步必须谨慎设计,过多的同步会导致性能下降。CUDA提供了丰富的同步机制,如线程块内同步函数__syncthreads(),帮助管理线程协作,确保数据一致性。

内存管理是CUDA内核编写中至关重要的部分。GPU拥有多级内存结构,包括寄存器、共享内存、全局内存、纹理内存等。合理使用不同类型的内存能极大提升内核的执行效率。共享内存是线程块内线程共享的高速缓存,访问速度远快于全局内存,适合存储频繁访问的数据。有效的内存访问策略,如内存访问对齐和避免内存银行冲突,可以最大化内存带宽利用率,降低访问延时。 优化CUDA内核性能还需要关注线程发散问题。

当同一个线程块中不同线程遵循不同的执行路径时,分支发散会导致执行效率降低。为减少发散,开发者应尽量避免条件分支语句,或者将分支划分到不同线程块处理。同时,合理的线程布局和任务划分也是避免发散的重要措施。 调试和性能分析工具对CUDA内核开发同样重要。英伟达提供了诸如Nsight Compute、Visual Profiler等工具,帮助开发者检测内核的性能瓶颈,分析内存访问模式,识别线程发散和资源竞争。这些工具能够通过实时数据反馈提供优化建议,显著提升开发效率和内核性能。

在实际应用中,CUDA内核已广泛应用于图像处理、科学计算、机器学习等领域。例如在深度学习中,卷积神经网络的训练过程大量依赖CUDA内核进行矩阵乘法和向量操作,通过优化内核设计,可以实现训练速度和推理效率的大幅度提升。同时,科学计算中的有限元分析、分子动力学等复杂数值模拟也依赖高效的CUDA内核来实现计算加速。 掌握CUDA内核编写需要一定的编程基础和并行计算知识。初学者应熟悉C/C++语言基础和并行计算理论,逐步学习CUDA编程模型以及内核设计原则。不断进行实践,结合性能分析工具进行调试和优化,将有助于积累丰富的经验,提高内核编写水平。

随着硬件的不断升级和CUDA生态的完善,未来CUDA内核编写将持续推动高性能计算领域的创新。开发者可以借助更先进的GPU架构和优化手段,设计出更高效、更复杂的并行算法,满足不断增长的计算需求。无论是科研院所,还是工业界,实现卓越性能的CUDA内核都将成为现代计算平台不可或缺的核心组件。 总之,CUDA内核编写不仅是GPU编程的核心技术,更是实现高性能计算的关键。通过合理设计内核结构、优化内存访问、减少线程发散以及利用强大的调试工具,开发者能够充分发挥GPU的计算潜能,推动各行业的技术进步和应用创新。在未来数字化时代,掌握CUDA内核编写无疑将为计算领域的专业人士带来巨大优势和机遇。

。