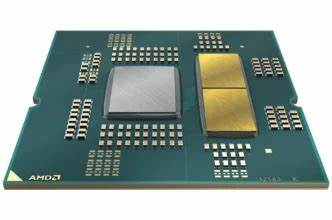

近年来,伴随着计算需求的快速增长和人工智能、大数据等新兴领域的兴起,处理器性能的提升已成为硬件厂商竞争的焦点。AMD作为全球领先的芯片制造商,通过其Zen架构的持续优化,实现了多年性能与能效的飞跃。即将到来的Zen 6架构,传闻将采用台积电最先进的2纳米(N2)和3纳米(N3P)工艺节点,这一消息引发了业界和消费者的广泛关注。 首先,了解Zen 6的制造工艺和设计布局有助于准确把握其性能潜力。Zen 6的CPU核心部分,即所谓的核心复合体芯片(Core Complex Die,CCD),计划采用台积电的2纳米制程。2纳米节点是目前业内最先进的工艺之一,具有极高的晶体管密度和能效比。

CCD是Zen架构的性能中枢,包括多个CPU核心,采用N2工艺将带来更高的主频、更低的功耗以及更强的热管理表现。 值得注意的是,Zen 6的客户端输入输出芯片(Client I/O Die,cIOD),也称为I/O芯片,预计将采用台积电的3纳米N3P工艺。这部分负责处理内存控制器、PCI Express通道和其他外围接口。使用3纳米制程主要考虑到成本和功耗的权衡。相比2纳米工艺,3纳米的制造难度相对较低,且针对I/O芯片的性能需求与CPU核心相比并不要求极限的能效和频率优势。 目前从业界多个知名爆料者处获得的信息显示,Zen 6不仅在工艺节点上进行了革新,芯片设计本身也朝着更高核心密度发展。

例如,面向高性能服务器的EPYC处理器版本将采用最多32核的Zen 6C架构芯片,其CCD依然基于台积电2纳米的N2P改进版本制造,专注于平衡性能和功耗。相较于桌面版12核CCD,这样的高密度设计要求极佳的工艺支持和良好的热控。 此外,对于顶级桌面处理器"奥林匹克峰会"系列,较早的爆料曾指出其可能会基于2纳米的N2X制程,这是一种针对高功率和极限性能优化的制造技术,有望支持处理器达到7 GHz的超高时钟频率。虽然N2X会带来更高的制造成本,但对于追求极致性能的发烧级玩家和专业应用场景,这无疑极具吸引力。 相比之下,I/O芯片采用3纳米N3P的决策十分明智。一方面,I/O芯片在整体功耗中占比相对较小,且其构造的逻辑单元多样,包括一些不易缩小的模拟电路。

另一方面,使用3纳米工艺可以降低成本,同时保持良好的带宽和延迟性能,使整体芯片的制造效率和良率得到保障。 值得一提的是,部分猜测认为采用3纳米N3P工艺的I/O芯片或将搭载部分低功耗的Zen 5 LP内核,用于移动平台的Zen 6"鳄鱼座"系列,提高系统空闲时的能效表现和响应速度。这种集成策略有助于提升移动端设备的续航能力和多任务处理的流畅度,为笔记本和平板设备的应用提供更多可能性。 以工艺制程为核心,Zen 6处理器的性能革新不仅局限于纯粹的主频提升和核心数量增加,更反映于能效比的全面优化。2纳米和3纳米节点的引入,使得芯片在同一功耗预算下实现更高性能,或者在同等性能表现下显著降低能耗,这对于日益注重环保和功耗的市场环境极为关键。 从市场角度来看,AMD选择与台积电合作,采用其2纳米和3纳米工艺,有助于保持和扩大其在与Intel的竞争优势。

Intel最近在工艺节点的发展上相对滞后,而台积电凭借先进制程和优良的产能成为全球半导体制造领导者,为AMD提供了坚实的工艺基础保障,从技术和供应链的多重角度强化AMD的竞争壁垒。 在未来应用场景中,Zen 6凭借更高的核心数和更强性能,预期在游戏、多媒体创作、科学计算、云计算和人工智能等领域展示强劲实力。尤其是服务器和数据中心,依赖高核心数和高能效比的处理器,Zen 6有望成为推动行业升级的重要动力。 不过需注意的是,台积电的2纳米和3纳米制造工艺计划要到2027年才开始大规模量产,这意味着Zen 6系列的正式发布及大规模商用还需等待一定时间。期间,AMD极可能通过继续优化工艺和架构设计,打磨产品细节,为用户呈现稳定且强劲的处理器性能。 AMD的Zen 6处理器计划正处于半导体行业技术迭代的前沿。

结合最新的台积电2纳米和3纳米工艺,Zen 6不仅仅是性能的简单跃升,更将推动整体计算平台向更高效、更强大的方向发展。2027年之后,随着新工艺的成熟和应用,PC和服务器市场或将迎来一波由Zen 6驱动的性能革命,为数字时代的计算需求提供坚实保障。 总而言之,AMD利用台积电先进的2纳米和3纳米制程为Zen 6打造的强大芯片组合,充分体现了现代芯片设计在性能、功耗和成本之间的精妙平衡,展现了技术创新对推动计算性能极限的重要作用。虽然距离Zen 6的全面商用还有一段时间,但相关消息已经让行业和消费者对未来的计算机体验充满期待。 。