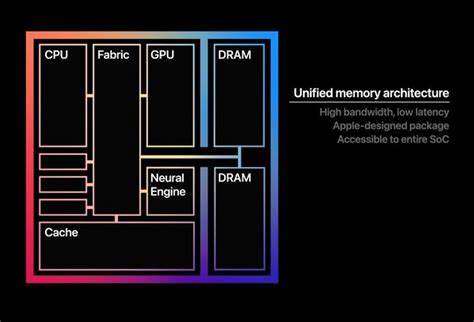

苹果M1芯片自推出以来,以其卓越的性能和能效比赢得了全球用户和开发者的高度关注。2023年升级版的M1芯片不仅在计算能力上有所突破,其内存排序模型的创新设计也为多核处理器架构带来了新的思考。内存排序模型作为现代处理器设计中的核心概念,直接影响着并发程序的行为、性能优化和系统稳定性,理解苹果M1芯片的内存排序模型对于软件开发者和硬件工程师来说尤为重要。 内存排序模型决定了在多核环境下不同处理器核心对内存操作的观察顺序。简单来说,它规定了写入和读取操作的执行顺序如何被其他核看到。对于并发程序而言,正确的内存排序保证了数据的一致性和正确性,而不同的内存模型在性能和编程复杂性之间进行了权衡。

苹果M1芯片采用了结合了现代RISC体系结构特点的内存排序策略,在保持较高性能的同时,兼顾了程序的易用性和系统的安全性。 2023年版本的苹果M1芯片基于ARM架构但经过深度定制,其内存排序模型体现了苹果在微架构创新上的独到见解。与传统ARM架构的弱内存顺序相比,M1在内存操作排序上引入了更严格的限制和创新的同步原语,既支持了强一致性模式,也允许在特定情境下采用更宽松的排序以提升性能。具体来说,M1芯片通过优化的缓存一致性协议和流水线管理,实现了高速缓存之间的高效数据同步,最大限度地减少了同步延迟和存储障碍的频率。 深入分析M1的内存排序模型,需要从其核心同步机制入手。苹果引入了一种兼顾性能和编程简易性的内存屏障方案,使得软件开发者能通过有限的同步指令集合,灵活控制内存操作的排序。

此外,M1芯片在硬件层面支持先进的乱序执行技术,结合智能的推测执行和动态调度,进一步优化了指令流水线并发度。通过这一系列技术手段,苹果的内存模型在保障程序语义正确的前提下,有效地提升了多线程程序的执行效率。 此外苹果M1的内存排序设计也体现了对并发安全的高度重视。现代多核系统中,数据竞争和内存一致性错误是导致程序崩溃和安全漏洞的常见原因。M1芯片通过硬件支持的同步原语,结合系统级的软件内存模型,确保了跨核访问的一致性检测和错误预防。这不仅降低了开发复杂度,也增强了系统的稳定性与安全防护能力。

从软硬件协同优化的角度看,苹果M1芯片的内存排序模型体现了苹果生态系统的深度整合优势。苹果控制了芯片设计、操作系统和编译器等关键环节,能够针对其内存模型进行细致的性能调优。macOS及其开发工具链充分利用内存排序的特点,自动优化线程调度和同步策略,为应用程序提供更顺畅的并发执行体验。同时,苹果在文档与开发者支持方面提供了详尽的指导,帮助程序员理解和正确使用M1的内存模型特性。 在实际应用场景中,苹果M1的内存排序优势尤为明显。高性能计算、多任务处理和实时图形渲染等领域均依赖于高效的内存访问和线程同步。

得益于M1芯片优化的内存模型,不仅显著减少了多核竞争开销,还提升了数据传输的吞吐量。这种设计让苹果设备在保证长续航的同时,依然能够提供媲美甚至超越传统x86架构CPU的强大计算能力。 展望未来,苹果M1的内存排序模型为下一代芯片设计奠定了坚实基础。随着多核处理器数量的增加和异构计算的普及,对内存一致性和同步机制的需求愈加复杂。苹果在新一代M系列芯片中的持续创新,将可能引入更加智能化的内存管理策略,如机器学习辅助的预测调度和自适应一致性模型,以进一步提升系统性能与开发效率。 总结来看,2023年苹果M1芯片的内存排序模型巧妙融合了严格与灵活的设计理念,通过软硬件协同优化实现了卓越的多核并发性能。

不仅保障了程序执行的正确性,也为并发编程提供了友好的开发环境。随着科技不断进步,这一模型的持续演进有望推动计算架构迈向更高的智能化和能效水平,对整个计算行业产生深远影响。 。