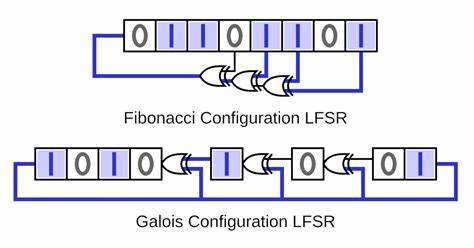

随着集成电路和FPGA技术的不断发展,工程师和设计师们开始重新审视传统CPU设计架构,试图在性能与资源占用之间找到更优的平衡点。基于线性反馈移位寄存器(LFSR)设计的CPU就是其中一项创新尝试。相较于传统的加法器驱动程序计数器,LFSR提供了一条门电路更少且逻辑复杂度更低的路径,为打造极简处理器提供了可能。本文聚焦介绍一款使用LFSR作为程序计数器的CPU,该设计不仅巧妙地缩减了硬件资源消耗,还能高效运行Forth语言,开拓了轻量型CPU运行高级语言的全新思路。 LFSR CPU的核心理念在于用一个线性反馈移位寄存器取代传统的程序计数器。传统的程序计数器一般依赖加法器实现递增,而加法器电路较复杂,占用更多芯片面积。

在FPGA等可编程逻辑器件中,虽然携带加法器的硬件单元(如配置逻辑块的传递链)相对高效,但在芯片面积和功耗方面的微小节省依然有其价值,如在7400系列芯片或定制晶体管电路中尤为明显。通过LFSR作为计数器,程序计数的方式趋向伪随机,但通过巧妙的设计,依然能保证程序的顺序执行和跳转逻辑的正确实现。 这款LFSR CPU构架采用16位数据总线和8位宽度的程序计数器,配合基于累加器的设计理念,使得整体指令集更加精简且功能完整。指令长度为16位,最高四位用于指令编码,其中最高位表明操作数是否为间接寻址。其指令集涵盖了主要的逻辑运算如XOR和AND,位移操作,加载与存储内存,条件和无条件跳转等,满足了实现Forth语言解释器所需的基础运算和程序控制能力。 通过使用LFSR提升设计的可调节性,设计者能在合成阶段灵活配置多项参数,如LFSR的多项式选择、长度、跳转条件,甚至是否包含加法指令等。

这种高度的定制能力使CPU不仅能适应不同应用需求,还能针对特定硬件平台优化资源占用和执行效率。 值得关注的是,尽管该设计舍弃了传统的加法器指令,这导致Forth代码的编写和执行稍显复杂且运行效率受到一定影响,但基于Forth语言天生的简洁和交互特性,整体的开发和调试体验依然保持良好。Forth作为一种解释型、栈式编程语言,适合运行在资源有限且结构简洁的微处理器上。LFSR CPU内置完整的Forth解释器,并预置了基本的字典和系统函数,使用户能够通过串口进行交互式编程,极大提升其灵活性和实用性。 从资源利用率来看,该CPU在Xilinx Spartan-6 FPGA上合成时仅占用29个切片,几乎与著名的PicoBlaze软核处理器相当,但不依赖特定厂商的底层资源,具有更好的跨平台移植性。虽然PicoBlaze支持中断及更丰富的指令集,LFSR CPU通过Forth语言提供了更为高级的编程环境,虽然性能上有所妥协,但带来了软件开发的便利性和系统调试的灵活性。

通过采用内存映射的输入输出机制,LFSR CPU能够高效实现外设的读写。负地址空间被划为I/O端口区,通过对高位设置的特殊地址进行访问,实现对UART等外设的控制和数据传输。此设计考虑到了FPGA的资源限制和扩展性,使得未来可以集成更多设备或构建多处理器矩阵系统,强化协同计算功能。 模拟阶段,该项目支持通过GHDL环境进行功能仿真,允许用户现场输入Forth命令、查询字典等,验证指令集的正确性和执行流程。值得一提的是,通过内置的调试模块和配置文件,开发者能方便地调整仿真参数、观察CPU状态,极大便利了研发验证工作。 展望未来,LFSR CPU拥有诸多发展潜力。

其可配置性强,能够根据应用需求进行硬件资源和指令集的权衡。可以考虑开发支持多端口存储器的版本,实现更高速的数据访问和并发操作。将Forth虚拟机代码分割存放于ROM和RAM中,可进一步加速系统启动和运行效率。同样,该设计具备移植为位串行处理器的潜力,有望进一步缩小芯片面积,适合更受限环境。 同时,将LFSR CPU与更多传统数字逻辑芯片(如7400系列)结合,设计基于真实物理IC的CPU原型,既能验证设计思路,也有望推动非常低成本和高可维护性的硬件平台出现。该方案对于教育、复古计算机研究和嵌入式系统原型开发都具备实际意义。

此外,将LFSR用作CPU程序计数器的理念,也促使工程师重新思考传统架构的瓶颈,寻找更具创新和节约资源的设计手段。LFSR本身不仅是一种计数机制,更广泛应用于伪随机数生成、循环冗余校验、内建自测试等领域。在CPU设计中引入LFSR元素,有助于打造功能更丰富且硬件利用率更高的处理器架构。 总体而言,基于LFSR的CPU设计在性能、资源、编程环境之间取得了平衡,展现出在专用和教学级嵌入式计算中独特的优势。它通过简单且可定制的指令集,结合Forth语言这一高度灵活且紧凑的编程环境,既实现了计算的必要功能,也降低了系统复杂度和开发难度。相信随着该项目的不断成熟,更多基于LFSR概念的创新处理器将涌现,为未来轻量级计算平台提供新的选择和参考。

。