在深度学习和高性能计算领域,矩阵乘法(matmul)是计算密集型工作的核心。Transformer模型中的线性变换、注意力机制和前馈网络都将大量计算集中在矩阵乘法上。要在现代GPU上实现接近理论峰值的matmul内核,必须理解硬件架构、内存层次、指令集以及高效的并行与数据移动策略。本文以NVIDIA Hopper H100为代表,从硬件到软件实现,系统性解析打造高性能matmul内核的关键技术。 GPU的性能来自两个基本要素:数据移动和算术运算。将数据从显存(HBM)高效移动到寄存器,并在寄存器或共享内存中以最小延迟反复重用,是达成高算术强度的前提。

GPU的内存层次包括设备内存(GMEM)、共享内存与L1缓存共用的SCRATCH区域、L2缓存以及寄存器文件。每一级从容量、带宽到延迟都有显著差异:寄存器最快但容量最小,HBM容量大但延迟与能耗高。对矩阵乘法而言,目标是把常访问的数据尽可能保存在靠近计算单元的高速存储中,减少GMEM的访问次数,从而把内核从带宽受限推向计算受限的区域。 共享内存(SMEM)由许多bank组成,典型设计为32个bank,每个bank以32位宽度提供数据。并发访问同一bank的不同地址会产生bank冲突,导致访问被序列化并显著降低吞吐。因此在内核实现时必须仔细设计索引与数据布局,避免或减小bank冲突。

值得注意的是,当多个线程访问共享内存的同一地址,硬件可以进行广播(multicast),这是利用共享内存进行数据复用的有效手段。 L1和SMEM在物理上共享存储阵列,而L1为硬件管理缓存,L2为全局缓存。了解cache的组织形式、组相联性及替换策略,有助于推测加载行为与miss率,从而调整访问模式。DRAM层面,HBM以行列结构存储数据,访问模式会影响DRAM行打开/关闭频率。访问连续地址可以获得更高带宽,非连续或跨行访问会造成DRAM与DDR接口效率下降,因此GMEM合并(coalescing)是高性能GPU编程的基石。 在指令层面,NVIDIA提供了虚拟ISA PTX与设备ISA SASS。

PTX作为可移植的中间表示便于长期兼容,但真正的性能微调常常需要观察或控制SASS级别的指令输出。理解PTX/SASS能帮助工程师确认编译器是否生成了预期的矢量化、内存指令和寄存器分配,以及哪里可以通过内联PTX或约束编译器选项来获得更优的指令序列。 设计高性能matmul通常从基本的并行分块(tiling)思想出发。将输出矩阵划分为块,令每个线程块(CTA)负责计算一个或多个输出子块,线程内或warp内再进一步划分任务,从而提高数据重用。早期的高性能实现使用warp-tiling思想:将每个线程块按warp或线程组分配输出子矩阵,提前将A、B的子块载入共享内存并进行局部计算。通过将内循环按块拆分为若干步,能够让局部的A或B在共享内存中被多次重用,从而显著提升算术强度(每字节的浮点运算数)。

随着架构演进,NVIDIA引入了Tensor Memory Accelerator(TMA)和张量核(Tensor Cores),这两项特性彻底改变了高性能matmul的实现方式。TMA支持GMEM与SMEM之间的异步搬运,并在搬运时对数据进行预设的"swizzle"变换以减少SMEM bank冲突。利用TMA可以把复杂的手工加载序列替换为少量的异步拷贝指令,从而释放CUDA核心用于计算。张量核在硬件层面对小矩阵乘累加做了强力加速,针对特定数据类型(例如bf16)和tile形状提供极高吞吐,现代内核几乎都依赖张量核来获取峰值性能。 Swizzle的本质是通过按位异或或其他地址变换,将原本在列方向或其他导致bank冲突的访问模式重新映射到共享内存的不同bank上,从而实现并行无冲突访问。实际的swizzle模式在实现上通常通过对地址的某些高位或低位进行异或掩码处理完成。

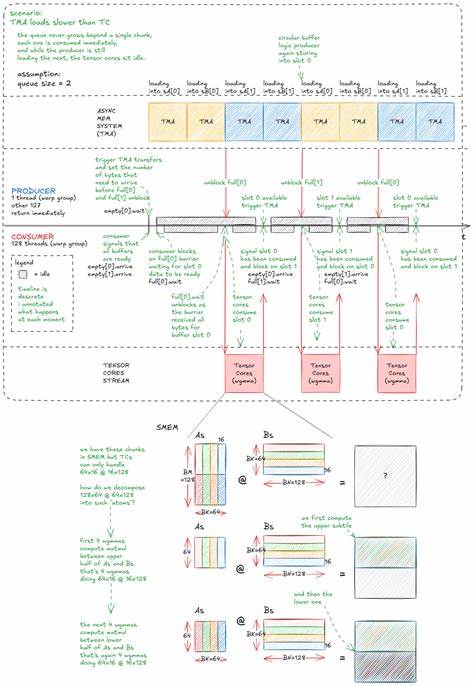

TMA在将数据搬入SMEM时会自动完成swizzle,随后在消费阶段读取的索引必须和swizzle的映射一致,或者在写回GMEM时让TMA恢复原始布局。 把TMA与张量核结合时,常见模式是:在每个CTA内部建立一个SMEM队列,每个队列槽由一对barrier(full与empty)或更轻量的同步机制管理。一个warp组(或少数线程)作为生产者负责通过TMA将A和B的子块投放到队列中,而一个或多个warp组作为消费者用张量核消耗这些子块并更新寄存器级的累加器。通过循环队列设计,与队列槽配套的异步字节计数保证消费者在开始计算前既有所有线程到达又确保数据已全部从TMA写入SMEM。生产者-消费者的分工允许在时间上重叠数据搬运与张量核计算,最大限度地减少资源空闲。 张量核的编程通常绕不开几条特殊指令,例如在Hopper上推出的wgmma.mma_async系列指令。

它们以warp-group为单位(通常为4个warp即128线程)做矩阵乘加,输入可以来自SMEM而结果聚合在浮点寄存器中。使用这些指令时需要遵守寄存器分配与同步语义:在发起mma_async之前使用fence语义确保寄存器或SMEM状态一致,发起若干异步mma后调用commit以形成一个group,最终wait可以阻塞直到该组的结果可用。通过把较大的矩阵乘分解为若干wgmma调用,结合重复执行可以把累加结果得到完整的输出子块。 在实现上,还需要面对寄存器压力、线程布局和occupancy之间的权衡。寄存器越多,单个线程能保存的累加结果越多,减少对共享内存或全局内存的中间写回,但更多的寄存器会降低每个SM可以同时驻留的CTA数量,从而降低遮蔽延迟的能力。合理选择每个CTA的线程数与tile尺寸是自动调优或经验调优的核心。

典型的优化包括把输出tile设计为接近正方形来提高数据重用,将每个线程的输出数量增大以提高算术强度,或通过增加消费者warp组的数量来分摊寄存器需求避免溢出。 流水线与持久化内核(persistent kernels)是提升末端性能的常用手段。持久化内核通常在每个SM上只运行少数固定数量的CTA,并让这些CTA在内部循环中处理多个输出tile。这样可以把输出写回GMEM的延迟与后续输入的加载重叠,尤其是在异步写回或利用TMA进行写回时效果显著。调度策略也影响缓存与L2访问局部性。使用空间填充曲线(例如Hilbert曲线)遍历输出tiles可以最大化邻近tiles之间的共享数据,降低L2和GMEM的重复加载,从而进一步提高整体带宽利用率。

在集群尺度上,Hopper引入的分布式共享内存(DSMEM)允许同一GPC内的多个SM共享部分SMEM资源与原子操作,从而把集群视为一个更大的协同计算单元。借助线程块簇(thread block clusters)和TMA的群播功能,可以在GPC内跨SM共享输入子块,显著降低对L2或HBM的重复访问。这类集群级别的优化要求细致的同步与分配策略,但在大tile或多SM合作场景下能够带来可观收益。 对编译器与底层指令的把控也能带来"零散的百分比"提升。通过观察PTX与SASS输出,开发者可以确认循环展开层数、矢量化负载(如LDG.128)、内存屏障插入点与无用指令。必要时使用内联PTX或特殊pragma来强制寄存器或指令序列安排,能把性能进一步逼近硬件的"speed-of-light"。

还要注意功耗与频率机制:在热或功率限制造成的频率下降情况下,理论峰值会随之下调,实际部署需考虑散热和功率预算以保持稳定的高吞吐。 最后,许多工程实践细节会在大规模部署时决定胜负。与cuBLAS等库的比较往往会受到输入尺寸分布、对齐方式、数据类型(bf16、fp16、fp32)、以及是否允许近似数学(如使用fast-math)等因素影响。对于特定尺寸的批量矩阵乘,定制内核通过自动调优到特定tile、tensor-core形状与队列长度,常能在实测中超过库函数少量到显著的性能百分比。在大型算力海量运行中,哪怕是1%的效率提升也能转化为千万美元级别的能耗或成本优势。 掌握高性能matmul的核心在于建立从电路物理到指令级再到并行算法的端到端理解。

理解DRAM与SRAM的差异、SMEM的bank细节、TMA与swizzle的作用、张量核的使用规范以及在寄存器、SMEM、并发线程之间的折衷,能够让工程师将数学上既简单又常见的矩阵乘法转变为近乎硬件极限的代码实现。随着GPU架构不断演进,新的异步引擎、存储层次和集群特性会继续推动实现方式与优化手段的演化,但那些关于局部性、带宽与计算重用的基本原则将永远是高性能编程的核心。 如果希望进一步实践,推荐从分析PTX/SASS开始,结合性能分析工具(如Nsight Compute)观察内核的带宽利用、寄存器使用和占用率,然后逐步引入TMA和张量核,构建生产者-消费者队列并尝试持久化内核与空间填充的调度策略。通过微基准与现实负载的反复迭代,可以把理论知识转化为在目标硬件上稳定可复现的高性能实现。 。