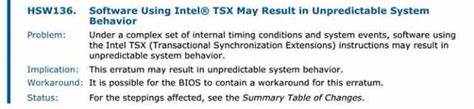

在多核处理器时代,如何高效管理并发执行成为计算机体系架构中的关键难题。传统的锁机制往往带来性能瓶颈,尤其是当线程争用资源时。为此,英特尔引入了Transactional Synchronization Extensions(简称TSX)技术,试图通过硬件支持的事务性内存执行,优化同步操作,提高多线程程序运行效率。然而,尽管技术起点颇高,TSX并未如期广泛铺开,甚至在部分处理器上被关闭或移除,这背后的原因引发了业界广泛关注和讨论。 TSX技术最初于2013年发布,包含两种实现模式:Hardware Lock Elision(HLE)和Restricted Transactional Memory(RTM)。HLE设计为对现有锁代码进行透明加速,允许程序员无需修改代码即可受益于事务性执行。

而RTM则提供更灵活的编程接口,开发者可以明确地控制事务边界,更有针对性地实现并行化操作。通过硬件级事务执行,TSX能够尝试将传统的锁操作转化为乐观执行,如果事务期间未检测到冲突,事务成功提交,从而避免昂贵的锁竞争和上下文切换。 这种设计带来的潜在性能提升对高性能计算、大数据处理和多线程服务器应用尤为重要,也使得TSX在技术发布时备受期待。厂商和开发者一度认为,TSX将革新并行计算的同步架构,推动软件利用多核优势迈上新台阶。 然而,理想与现实往往有落差。TSX的广泛应用遭遇了多个严重挑战。

最直接的障碍是稳定性和安全问题。2018年,研究人员揭露了针对TSX的多种硬件漏洞,部分被归类为侧信道攻击的利用途径,能够通过微架构泄露敏感信息。这些安全隐患一度导致英特尔暂停部分处理器的TSX功能,甚至在新一代芯片中弃用该技术。 另外,TSX在实际应用中的性能表现并非一直优于传统锁技术。事务执行的成功率取决于冲突率和事务大小,频繁的事务回滚会消耗宝贵资源,反而拖慢程序运行。软件层面也面临挑战,编程模型需要适应事务性执行的逻辑控制,开发复杂度提升,且调试和测试难度增大。

在产业实践中,许多操作系统和中间件对TSX的支持保持谨慎,核心组件并未大量采用该技术。一些尖端数据库系统和并行算法尝试过基于TSX的优化,但整体市场认可度不足。加之英特尔在其处理器产品路线图中对TSX持保留态度,导致开发生态热度下降。 基于以上因素,TSX没有成为英特尔CPU的标准配置。尽管如此,硬件事务性内存概念并未被完全抛弃,研究界和部分硬件厂商仍在探索更安全、高效的实现方法。例如,ARM架构提出了异构多核支持和事务性内存扩展,IBM POWER处理器也具备类似的事务性机制,反映事务性内存作为优化并发同步的重要方向。

展望未来,TSX的教训为业界提供宝贵经验。安全性、稳定性依旧是硬件创新必须面对的核心考量。事务性内存技术若能突破现有瓶颈,有望进一步推动并行编程范式转型,提升多核利用率和应用性能。与此同时,软件工具链的完善、开发者教育以及应用场景的精准定位同样关键。 总结来看,Intel TSX代表了处理器设计和并发控制技术的一次大胆尝试,揭示了硬件支持同步机制的巨大潜力与复杂风险。虽然其未能成为主流且被逐步弃用,但TSX推动了相关领域的技术进步和安全研究,成为计算机体系结构发展史中的重要篇章。

未来,借鉴TSX的经验教训,硬件事务性内存技术仍有望持续演进并找到新的突破口,助力构建性能更优、更加安全的多线程计算环境。 。