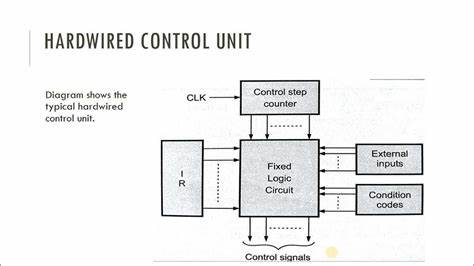

硬连线控制单元作为计算机体系结构中的核心组件之一,肩负着指令的译码与控制信号生成的重要任务。相比于微程序控制单元,硬连线控制单元以其高速与直接控制优势被广泛应用于高性能计算系统中。然而,在设计硬连线控制单元时,工程师面临着诸多挑战,需要遵循科学的设计流程与方法,确保其高效、稳定和可靠。本文将深入剖析硬连线控制单元设计中的关键技巧与实践,帮助设计人员掌握核心原理,提升设计能力。硬连线控制单元的作用在于将指令的操作码转换为相应的控制信号,直接驱动计算机内部各部件的协同工作。其设计的复杂性主要体现在所需控制信号的数量庞大以及信号生成的逻辑复杂度高。

首先,设计人员需对目标指令集架构有深刻理解,包括各条指令的执行流程、所需操作信号及其时序要求,只有了解清楚这些基本信息,才能设计出合理的控制逻辑。其次,确定控制逻辑的表达形式是设计的关键环节。常见做法是将控制信号与当前指令状态组合起来,使用逻辑门电路实现对应关系。采用正规且系统化的设计方法,能够减少错误和冗余,提高电路简洁性。例如,布尔代数的简化技术、卡诺图优化都能帮助设计者优化逻辑表达式,从而降低门电路数量,节约硬件资源。硬连线控制单元设计不可忽视时序控制这一关键因素。

不同控制信号之间不仅仅需要保持正确的逻辑组合关系,还必须严格按照时钟脉冲进行同步。设计时应合理划分控制周期,确保各阶段信号的生成、传输与执行彼此协调,避免出现竞态或冒险现象。采用有限状态机(FSM)方法,有助于对控制信号时序进行科学管理,将复杂的控制状态分阶段实现,使设计更具可控性和可维护性。此外,设计人员进行硬连线控制单元设计时,还应积极借鉴自动化设计工具,借助硬件描述语言(HDL)和逻辑综合工具实现设计的快速验证和优化。通过仿真测试可以及时发现逻辑错误或时序冲突,确保设计的准确性与稳定性。设计过程中,模块化思想同样重要。

将控制逻辑划分为多个功能模块,不仅便于调试维护,还能提高设计的复用性和扩展性。例如,将指令译码单元、时序生成单元和控制信号分配单元分开设计,有效降低模块间耦合度,提升整体结构的清晰度。硬连线控制单元在设计时还需充分考虑可扩展性。随着指令集的发展需求,新增指令和控制信号成为不可避免的趋势。采用灵活的设计机制,预留扩展接口与兼容机制,有助于未来升级和功能增强,延长硬件寿命,降低后续维护成本。安全性和容错性设计也是硬连线控制单元不可忽视的方面。

由于其控制信号直接影响计算机行为,信号干扰或设计缺陷可能导致系统功能异常。利用冗余设计、错误检测纠正技术、信号滤波措置等方法,能有效提升系统可靠性,保障核心控制单元的稳定运行。针对现代复杂系统,硬连线控制单元的设计已趋于更加复杂和多样化。设计人员应结合具体应用场景,综合考虑性能需求、功耗限制及成本预算,制定科学合理的设计策略。在高性能需求场合,强调信号生成的速度和同步性;而在低功耗设备中,则优先优化电路设计,降低功耗消耗。硬连线控制单元的设计并非一蹴而就,需经过反复迭代与验证。

完善的设计流程包括需求分析、初步设计、逻辑实现、仿真验证、物理布局及最终测试,每一步都需细致严谨。积累丰富的设计经验和教训总结,是提升硬连线控制单元设计水平的宝贵财富。总体来看,硬连线控制单元作为计算机控制架构的基础模块,设计技巧涵盖逻辑优化、时序控制、模块划分、可扩展性、安全性和自动化辅助等多个维度。设计人员应结合理论基础与实践经验,不断探索创新方法,推动硬连线控制单元设计向更高速、更可靠、更智能的方向发展。通过科学合理的设计策略与技术应用,硬连线控制单元将持续发挥其在现代计算机体系结构中的重要作用,助力实现高效能计算和智能化控制目标。 。