在数字硬件设计领域,硬件描述语言(HDL)一直是桥梁,将设计理念转化为具体且可行的电路实现。传统上,Verilog和VHDL是占主导地位的两大语言,支撑着数十年的硬件设计与验证工作。然而,随着设计复杂性的增加和速度需求的提升,设计者们逐渐希望寻求更高效、更直观、且便于管理复杂性的工具。SUS,作为一款新兴的硬件描述语言,正是在这一背景下应运而生,专注于为高性能同步硬件设计提供强有力的支持和创新体验。SUS HDL不仅承袭了现有语言在硬件电路建模方面的优势,更在语法简洁性、时序管理、元编程能力等方面带来了显著突破,令其在硬件设计领域具备独特竞争力。 首先,SUS语言的核心理念是回归寄存器传输级(RTL)设计本质,强调硬件设计中的同步逻辑表达和低延迟路径的准确建模。

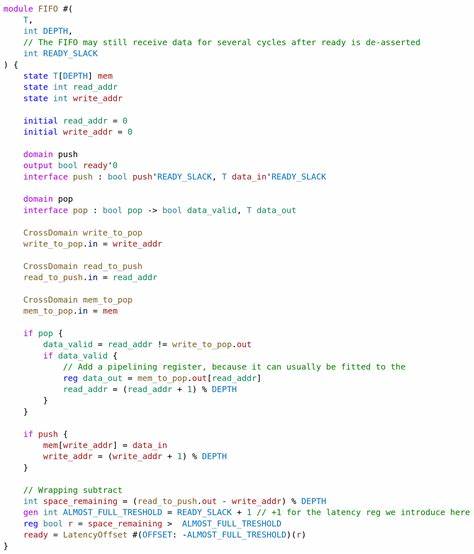

与传统HDL相比,SUS最大的亮点之一是引入了延迟计数(Latency Counting)机制。这个机制使得编译器能够自动追踪设计中各信号和模块的时序延迟,从而帮助设计者更加精准地理解和优化流水线结构。时序和流水线设计是硬件设计中最具挑战性的环节之一,时序错误可能导致严重的功能异常和性能瓶颈。通过Compiler内置的延迟管理,SUS显著降低了设计和调试复杂度,开发者能够更专注于算法优化和整体架构设计,而不是陷入繁杂的时序修正工作。 其次,SUS被设计为一个便于“玩转”和反复调整的开放环境。传统的硬件语言通常较为死板,难以快速试验或迭代新想法。

SUS编译器通过实时跟踪硬件元素属性和参数变化,在代码编辑器中提供即时反馈和辅助,使设计者在开发过程中获得可视化的设计信息和性能指标。这种交互式设计体验不仅提升了开发效率,也激励设计者发挥创造力,在硬件结构、模块组合等方面进行大胆尝试和优化。 与此同时,SUS强调对硬件设计的全面控制。如果设计者能够用同步逻辑图表现硬件结构,那么便可以用SUS精准表达这一设计。不同于某些抽象层过高、强制特定设计范式的语言,SUS拒绝对设计风格加以限制,而是专注于帮助设计者透彻描述同步数字电路逻辑,提供灵活性与底层可控性的完美平衡。因此,对于那些有成熟硬件设计经验并追求精细控制的工程师来说,SUS是理想的工具。

SUS的另一个独特优势在于其强大的元编程能力。该语言支持在编译阶段执行代码,这意味着设计者可以利用语言本身生成复杂的查找表(LUT)或设计参数化模块。网络加法树的示例展示了这一能力:通过参数化宽度和值数组递归构建加法树,编译器自动生成对应硬件模块。元编程不仅减少了重复代码,提高了设计模块的复用性,也为设计自动化和算法驱动的电路生成提供了坚实基础。 从设计哲学来看,SUS致力于成为一种比Verilog和VHDL更直观和简洁的语言。它的语法设计偏向薄层叙述,避免对设计师施加过多框架或约束,让硬件设计的本质复杂度得以透明地体现和管理。

SUS并不试图掩盖硬件设计的复杂性,相反,它通过易于理解的代码结构和工具支持,帮助设计者以更系统化和可控的方式驾驭硬件架构。 然而,SUS语言对硬件的同步性提出了明确要求。所有设计必须是同步时钟驱动的,异步设计无法用SUS表达。这一限制意味着SUS更适合FPGA和部分ASIC设计等强调同步逻辑的场景,而不适用于需要跨时钟域复杂通信或异步电路的项目。虽然这一限制减少了部分应用范围,但对绝大多数现代高性能数字电路而言,同步设计依然是主流,因此SUS依然能够满足绝大多数设计需求。 从功能层面来看,SUS不仅提供基础的语法和时序跟踪功能,还预计在未来版本中引入更加丰富的特性,如多时钟域支持、更智能的资源管理和综合优化工具。

这些规划表明,SUS项目团队正在积极响应社区反馈,致力提升工具链的完整性,打造一套覆盖硬件设计全流程的解决方案。 对于想要快速入门SUS的设计者来说,项目提供了丰富易懂的学习资源,包括40分钟即可掌握核心概念的入门视频,以及活跃的社区支持平台如GitHub和Discord。设计者可以借助这些资源迅速了解SUS的语法特性、使用方法和最佳实践,在实际项目中迅速应用。 在硬件设计领域,准确、简洁且强大易用的HDL语言不仅能提升设计效率,更是推动技术创新和产业升级的重要工具。SUS作为一款富有创新精神的硬件描述语言,融合了先进编译技术和用户体验设计,有望成为未来高性能同步硬件设计领域的主流选择。它不仅方便硬件专家以更低的门槛开发复杂电路,也为硬件教育和研究提供了极具吸引力的实验平台。

随着设计规模不断扩大和性能需求日益严苛,SUS语言的优势将愈加显著,值得每一位硬件设计工程师和学者深入了解与实践。通过拥抱SUS,设计者或许能够更好地应对未来硬件挑战,加速创新步伐,打造更为高效且可靠的数字世界。