随着计算机处理器技术的不断发展,微架构性能优化成为提升计算效率的关键。然而,这些优化不仅带来了性能提升,也催生了难以预料的信息泄漏风险,尤其是在微架构层面。这些潜在的安全隐患往往被称为微架构泄漏(Microarchitectural Leakage),它们通过隐蔽的时间差异或其它侧信道影响CPU执行路径,从而泄露敏感信息。针对这个日益严峻的挑战,ETH Zurich的计算机安全团队研发了MileSan,这是一款基于差分硬件/软件污点追踪的RTX级别微架构泄漏检测工具,开创性地推动了硬件安全检测技术的前沿。微架构泄漏与传统安全隐患的最大区别在于,它们并非直接来自指令集架构定义的行为,而是源自底层硬件实现中的性能优化,这些优化导致了信息流超出架构可观测范围。简言之,虽然CPU官方的指令集架构(ISA)限定了信息流向,但微架构内诸如缓存、分支预测、流水线等机制引入额外信息流,从而衍生出这些泄漏。

MileSan的核心理念正是基于比对两者之间的信息流差异,捕捉那些只有在微架构层面可见的多余信息流,从而实现对泄漏的自动检测和定位。传统的微架构泄漏检测工具存在严重的过拟合问题。它们在评估过程中往往依赖于针对已知硬件结构的小范围人工标记,或者依赖于有限的攻击模板与测试种子,无法生成足够多样化的测试用例,也难以发现未知漏洞。此外,这些方法通常针对特定类型的漏洞,如侧信道定时攻击或瞬态执行漏洞,导致检测范围受限。相比之下,MileSan采用无偏见的差分污点追踪机制,突破了传统检测的限制。差分污点追踪技术包括软件层面的静态污点追踪和硬件层面的动态污点追踪。

软件污点追踪借助程序语义和ISA规则,准确描述架构信息流的位置及传播路径。而硬件污点追踪则基于CPU微架构的RTL级模拟运行,动态捕捉实际信息流。通过对比两者的污点传播情况,MileSan能够发现那些未被架构认可,却在微架构层面产生的污点扩散,指示出潜在泄漏点。这一机制极大地提升了检测的准确性和普适性,避免了误报及漏报。为了完善整体检测能力,团队打造了RandOS,一款基于MileSan的随机操作系统风格微架构模糊测试引擎。RandOS能够自动生成多样化、复杂且具有确定性污点传播路径的程序,这些程序涵盖不同权限级别和地址空间布局,模拟真实操作系统环境中的安全场景。

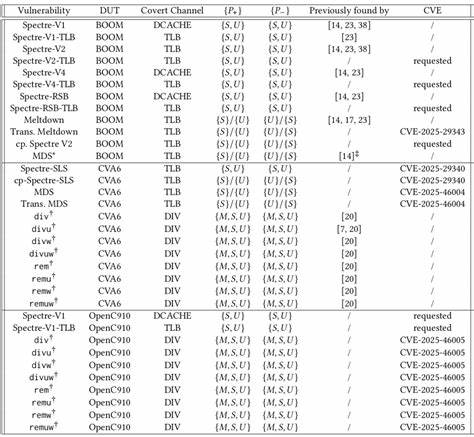

通过执行这些程序,MileSan利用差分污点追踪技术检测程序对机密数据的潜在泄漏。RandOS不仅能生成多种安全域之间交互的攻击面,还能轻松定位造成泄漏的架构及微架构代码段,极大地加速漏洞发现与分析过程。采用MileSan与RandOS组合的验证针对多个开源RISC-V处理器展开。实验共计辨识出了19个新的微架构漏洞,其中13个漏洞已被授予公共编号(CVE),涵盖了包括常见定时攻击和瞬态执行漏洞在内的多个类别。这证明了MileSan方案在实际CPU设计安全验证中的高效性与广泛适用性。此次成果不仅提升了处理器设计厂商识别和修复微架构安全风险的能力,更为未来架构的稳健性奠定基石。

同时,这也推动了基于符号执行与污点传播相结合的多层安全分析新范式。虽然MileSan当前主要实现针对RISC-V指令集,然而其原理和方法论普适性强,完全可推广到其他主流处理器架构的微架构分析中。未来在持续工程投入下,有望成为各大CPU设计企业预硅安全审计的标配工具。MileSan内部解决了信息流较难追踪和污点爆炸的问题。一般情况下,程序计数器(PC)因涉及所有控制流分支,极易导致污点爆炸,使得检测异常复杂。针对这一点,MileSan通过差分设计有效抑制该问题,仅同步多余的信息流,从而聚焦于架构与微架构差异,减少误判和性能开销。

这种设计意义非凡,为大规模硬件验证开辟了新思路。使用MileSan的开发者应认识到其检测结果对应的是基于当前测试程序集的相对安全性保证。也就是说,由于测试空间非穷尽,仍有可能存在某些未被测试覆盖的微架构泄漏。保证全面安全还需结合多样化的程序生成器和攻击模拟,为硬件漏洞提供更为充分的覆盖。随着CPU微架构愈发复杂,性能优化与安全边界的平衡变得更加关键。MileSan为这一难题提供了技术突破口和实践路径,将差分污点追踪从软件安全领域成功移植到硬件设计验证领域,推动了微架构安全检测的自动化和高效化进程。

预期这一技术能够加速安全硬件的研发,减少因隐蔽漏洞带来的威胁风险。综上所述,MileSan通过差分硬件/软件污点追踪的创新手段,精准捕捉超出架构范畴的微架构信息流,揭示潜在的时序侧信道和瞬态执行漏洞,助力处理器安全生态系统升级。结合RandOS模糊测试框架,能够覆盖丰富的安全场景与权限交互,成就了一个强大且泛用的预硅安全分析平台。随着这项技术的进一步推广和完善,未来计算机硬件设计必将在保障信息安全方面迈出坚实而关键的一步。 。